這麽好玩的問題,沒人回答說不過去。不懂電子元件的碼農我要強答一發了。太學術的我不會,你們也聽不懂。所以臭不要臉非常不嚴謹地科普一記。說錯不許打我。

另外關於這個問題,推薦【

編碼 (豆瓣)】這本書,挺薄的。當【十萬個為什麽】看,好奇的同學一晚上就能搞明白。

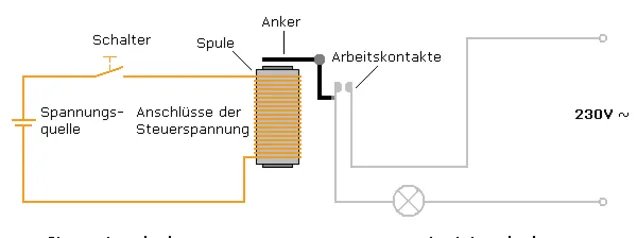

第一季 繼電器先不要扯什麽圖靈,馮諾依曼這些先賢。因為他們都太遙遠。電腦一切計算的源頭其實是源自一個非常非常中二的東西: 「繼電器(Relay)」 。繼電器是什麽鬼?看下圖,

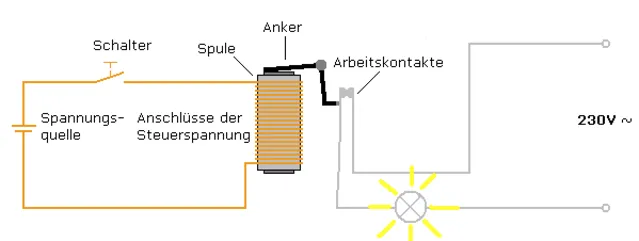

其實就是一個線圈利用電磁感應做成的電磁鐵。原理和「電報機」一樣,當開關閉合,黃色電路通電,線圈是金屬棒變成磁鐵,吸引中間的小開關(Anker),接通右邊灰色的電路,點亮燈泡。

簡單說,就是你在家一按開關,隔壁老王家的燈亮了。

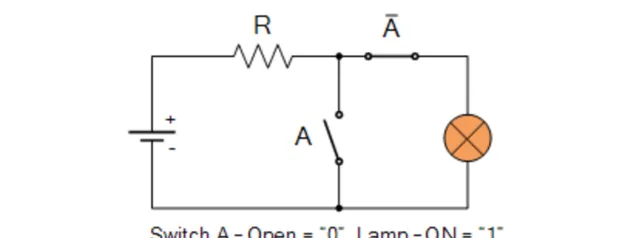

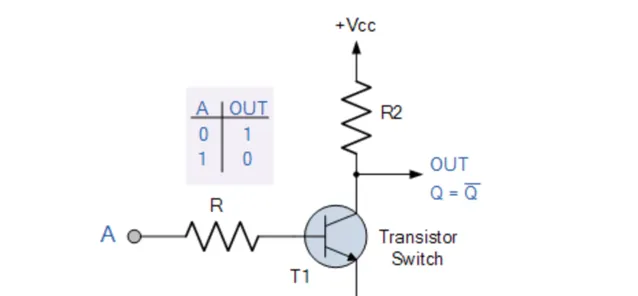

第二季 「反相器」和「非門」為什麽說繼電器是個很中二的東西?因為這不就是開關嗎?我按了它才亮,不按絕對不亮。但CPU真就是這貨發展而來的。它的變種就開始好玩了。最簡單的一個變種,就是「反繼電器」,或者叫 「反相器(Inverter)」 。就是隔壁老王家的燈本來是亮著的,我手上的開關一按,燈就滅了。

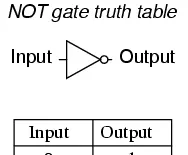

"反相器"到了現代電腦裏,就叫做 「非門(NOT Gate)」 。本來開關T1是接通的,Output是1(5V高位電平)。一旦閉合開關T1,電路中斷,輸出變為0(1V低位電平)。

「非門」用下面這個符號表示。簡單說,就是輸出永遠和輸入是反的,輸入1,輸出就是0。輸入0,輸出就是1。

第三季 邏輯閘家族

第三季 邏輯閘家族

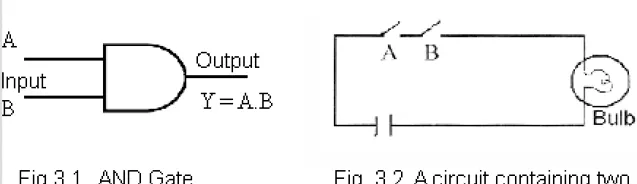

和「非門」一樣,我們能得到一堆其他特性的門。比如,「 與門(AND Gate) 」,就是兩個開關串聯。必須兩個開關同時閉合,燈泡才能亮。

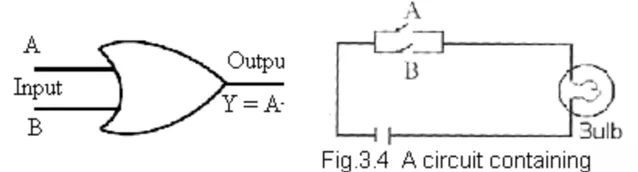

「或門(OR Gate)」 ,兩個開關並聯,只要其中一個開關閉合,燈泡就會亮。

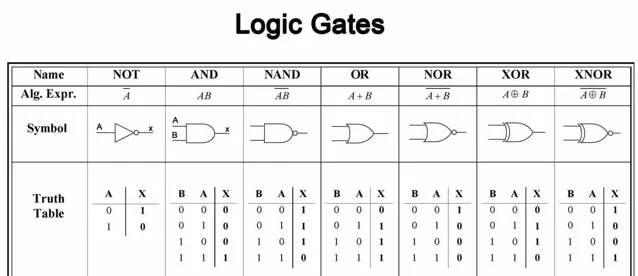

長話短說,下圖是所能得到的幾個基本 「邏輯閘(Logic Gates)」 。

雖然看上去比較復雜,但「邏輯閘」在本質上和之前講的「繼電器」都是「控制電路」。 或者說都是我手裏握著控制老王家花式吊燈的各種開關。 老王一定很郁悶。

第四季 邏輯邏輯閘雖然被我說得很淳樸,就是控制隔壁老王家吊燈的開關。但其中卻可能蘊含著人類大腦,甚至是這個世界終極奧義的一部份: 邏輯(Logic) 。這也是為什麽它被叫做邏輯閘。

愛因史坦曾說過:

世界上最不可思議的事情,就是這個世界是可以被「理解」的。簡直是細思極恐有木有!最簡單的例子,亞里斯多德給出的經典 「Barbara」三段論 :

如果所有人(M)都是必死的(P),(大前提)並且所有希臘人(S)都是人(M),(小前提)

那麽所有希臘人(S)都是必死的(P)。(結論)

數學上,一個 形式系統 (Formal system)的野心就是想透過一組公理,和邏輯推理過程,來描述和證明我們的客觀世界。說到這裏我們電腦的祖師爺們就都出來了:萊布尼茲,康托爾,布爾,圖靈,等等等等。著名的圖靈機就是在這個議題的爭論中無心插柳的副產品。這個主題無法展開。感興趣推薦看【

邏輯的引擎 (豆瓣)】這本書。這裏只舉一個最簡單的 「布爾代數(Boolean algebra)」 的例子:

我喜歡(長頭發)的(不是)(蛇精臉)的女生用布爾代數來表示就是:

長頭發 AND ( NOT 蛇精臉)說到這裏,是不是和前面說的邏輯閘聯系起來了?

第五季 邏輯電路但是邏輯是邏輯,繼電器是繼電器,就算上面的花式繼電器也是繼電器。把邏輯和繼電器聯系起來的是一位不得不提的大師, 克勞德·艾爾伍德·夏農 ( Claude Elwood Shannon) 和他的那篇史上最牛碩士論文 : 【繼電器與開關電路的符號分析】 。 絕對最牛,沒有之一!

還是之前那個例子:

我喜歡(長頭發)的(不是)(蛇精臉)的女生如果:

A代表:長頭發B代表:蛇精臉

那我喜歡的女生就可以寫成一個布爾函式:

Love = A\bar{B}

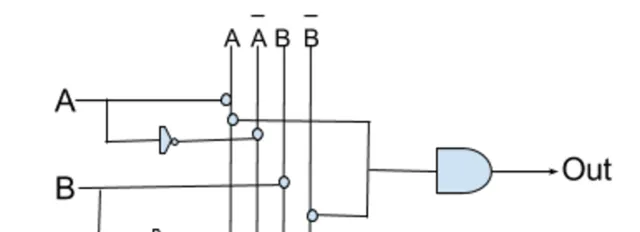

把一個邏輯命題用符號寫成一個公式有什麽用呢?那是因為這樣就可以很方便地轉換成一個「 邏輯表決器」, 如下圖。

原理很簡單,當A=1時,縱向的A匯流排為1。當A=0時,\bar{A} 匯流排輸出1。B也是如此。最後的輸出線搭在A匯流排和\bar{B} 匯流排上,用個與門連線。所以只有當A的輸入為1,B的輸入為0時,Out才為1,代表我能接受這個女孩。不信大家可以人肉推演一下。

理論上任何布爾函式,都能轉換成上面這樣的表決器。就好像電路有了人類邏輯思考的能力。

第六季 「圖靈機」和「累加器」總算要說到電腦的祖師爺 圖靈(Turing) 了。圖靈機模型,相比上面說到的邏輯電路,要多一個 「記憶體」 。因為根據圖靈機模擬人類計算時大腦的工作狀態的模型,人類的任何計算都可以抽象成一個機械化的過程。

考慮5+7=12這個加法。5加7等於12,寫下2,然後心中默記產生一個進位。最終寫成12。

5

+ 7

-----

12

換成二進制,是一個道理,

0000

0101

+ 0000

0111

-------------

0000

1100

其中每一位的加法還是能分解成兩個動作:

-

同一位的兩個數位相加

- 如果當前位結果大於1,則向前進一位

第一個動作可能的結果(真值表)有:

0 XOR 0=01 XOR 0=1

0 XOR 1=1

1 XOR 1=0

這個真值表和一個簡單的「 異或門 」是一致的。

第二步進位,只有1+1才需要進位1,所以真值表如下:

0 AND 0=01 AND 0=0

0 AND 1=0

1 AND 1=1

這和「 與門 」的真值表是一致的。

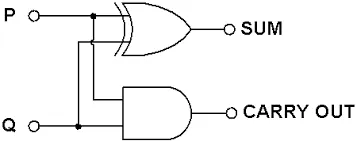

所以把一個 「異或門」 和一個 「與門」 組合到一起,就構成了一個 「一位半加器」 :

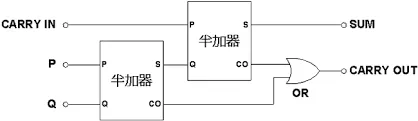

但事實上一位半加器只適用於末位數的加法。高位的二進制加法需要考慮3個輸入,就是還需要額外考慮上一位得到的進位。這個過程可以用兩個半加器來完成。

兩個半加器組合起來,構成一個完整的 「一位全加器」 。

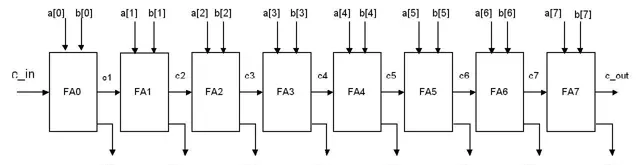

把8個這樣的一位全加器組合起來,就構成了一個 「八位全加器」 :

從最末尾開始相加,剛才的5+7:

0000

0101

+ 0000

0111

反過來就變成:

1010

0000

+ 1110

0000

-------------

0011

0000

把最初的進位 c_in 設為0,得到的結果反過來就是: 0000 1100 = 12 。

至此,電腦好像擁有了人腦的部份智慧。既然一組邏輯閘,能計算加法,就一定能做減法,乘法,除法,和其他計算。

第六季 寄存器加減乘除遠遠不是邏輯閘能做的全部事情。實際上電腦裏出了硬碟,風扇,電池,其他幾乎全是由邏輯電路和邏輯閘組成的,包括我們說的 記憶體 。說記憶體先要說一下寄存器。這東西我覺得是比CPU更神奇的一個東西。絕對是一大黑魔法。用幾個簡單的邏輯閘,就能在不斷電的情況下一直」記住「上次的輸入值。

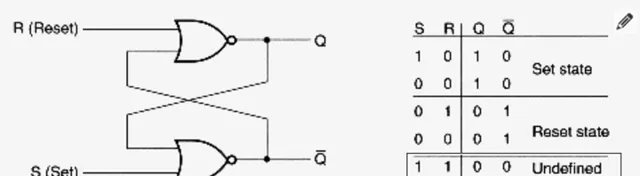

最簡單的儲存部件叫 「SR鎖存器(Latch)」 。其實就是兩個「或非門」。

再看一眼或非門的真值表:只有兩個輸入都為0,才輸出1。

0 NOR 0 = 11 NOR 0 = 0

0 NOR 1 = 0

1 NOR 1 = 0

其中具體電流怎麽透過互相賽局達到穩態的細節就不展開了。總之這個黑科技的最終效果就是:

假設初始狀態都是零:S=0, R=0。輸出Q=0,\bar{Q} =0當S端給個訊號1,輸出Q=1,\bar{Q} =0

當S端變回訊號0,輸出還是保持Q=1,\bar{Q} =0

也就是說,這個元件記住了之前S端的輸入1。直到我們把R端設為1,輸出Q才變回0。

雖然這個SR鎖存器離我們真實的「RAM記憶體」還很遙遠。但讓邏輯閘產生「記憶」的核心邏輯穩態鎖就是這麽簡單的兩個或非門。

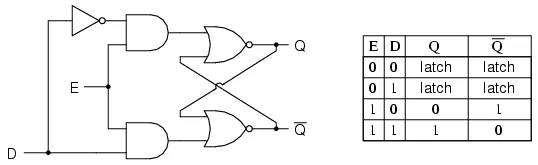

當我們把SR鎖存器的兩個輸入端捏合成一個D輸入端,再加上一個由時鐘訊號控制端E,就得到一個更高級的 「時序D鎖存器」 。如果不想頭痛,只要記住 這是一個能在時鐘開關E開啟的情況下,記住D輸入端進來的訊號的裝置 。之後我們一直可以從Q端得到之前D端的值。

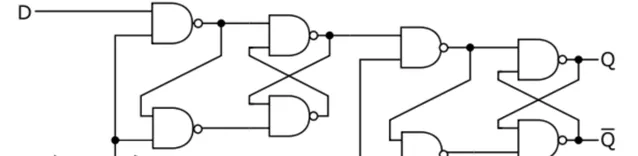

如果再復雜一點,把兩個相反的時序D鎖存器組合在一起,就能構成一個 「D觸發器(D Flip Flop)」 :

觸發器和之前的鎖存器的區別是,只有當時鐘訊號處在上升沿(從1V向5V躍遷)的一瞬間,D端的輸入值才能寫入觸發器。並在隨後的時間內,只要沒有新的D輸入寫入,Q一直保持這個值。

D觸發器離我們的記憶體就沒那麽遠了。只要再套上一個用於尋址的「解碼器」和之前說過的「選擇器」,就能實作從特定一組觸發器中讀取數據的效果啦。

所以我們都知道CPU需要時鐘來同步時序電路。但這個晶振時鐘並不是像想象的那樣直接作用在 ALU(邏輯運算單元) 上,而是透過寄存器來實作時序控制。感興趣的可以看這個回答:

為什麽CPU需要時鐘才能工作? - 胖胖的回答第七季 硬體 V.s. 軟體

雖然,幾乎所有計算都能設計出一個專門的邏輯運算器。但這樣做似乎並不明智,否則邏輯部件的數量將以指數級增長。一個合理的方案,應該是用硬體實作部份必須的基礎計算功能,然後已軟體的方式,利用基礎計算單元,完成復雜計算。

就好像做乘法,不需要設計一個專門的「乘法器」,而是重復多次加法運算即可。這裏就是所謂軟體開始介入的地方。也就是所謂的「演算法」開始放發揮作用,雖然並不是硬體無法勝任這項工作,而是把復雜性交給軟體來處理似乎更合理。

從此,在硬體這棵樹上,開出了軟體這朵花。也就有了」程式設計師「這個嚴重傷害頸椎和腰椎的職業。