謝邀。先說結論,多核CPU和多CPU的區別主要在於效能和成本。多核CPU效能最好,但成本最高;多CPU成本小,便宜,但效能相對較差。我們來看一個例子:如果我們需要組成一個48核的電腦,我們可以有這麽三種選擇:

- 把48個核全部做到一個大Die上,Die很大。這個Die加上一些外圍電路組成一個單Die多核CPU。

- 弄4個小Die,每個Die 12個內核,每個Die很小。把這4個Die,加上互聯總線和外圍電路,全部封裝(Packaging)到 一個 多Die多核CPU中。

- 還是弄4個Die,每個Die 12個內核,每個Die很小。每個Die加上外圍電路封裝成一個單獨的CPU,4個CPU再透過總線組成一個多路(way/socket)系統。

我們來看看他們的效能差距和成本差距。

效能差距

為了很好的理解三者之間的區別,我們透過一個生活中的場景分別指代三種方式。 我們想像每個Die是一棟大樓,Die裏面的內核們,記憶體控制器們、PCIe控制器們和其他功能模組是其中的一個個房間。數據流和指令流在它們之間的流動看作房間裏面的人們互相串門,這種串門的方便程度和走廊寬度決定了人們願不願意和多少人可以同時串門,也就指代了數據的延遲和頻寬 。

好了,有了這種方便的比喻,我們來看看三種情況分別是什麽。

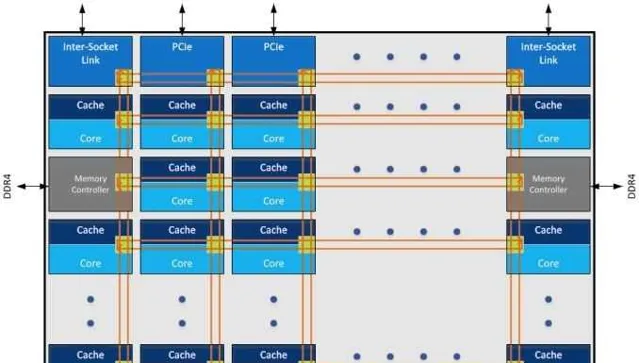

48核的大Die是Intel至強系列的標準做法:

這種方法就是既然需要這麽多房間,業主有錢,就建一個大樓,每層都是 超級大平層 :

走廊眾多,這裏堵了,換個路過去,反正方向對了就行,總能到的。所以人們可以很方便的串門,也可以有很多人同時串門。所以延遲小,頻寬高。

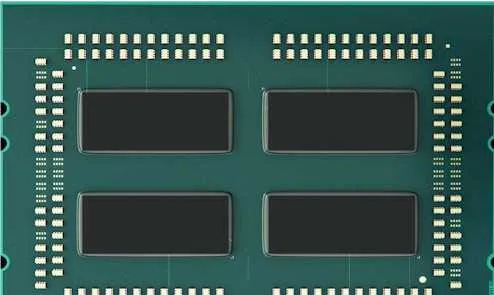

一個CPU pacakge裏麪包了4個小Die的做法是AMD的標準做法,也有部份Intel也這樣:

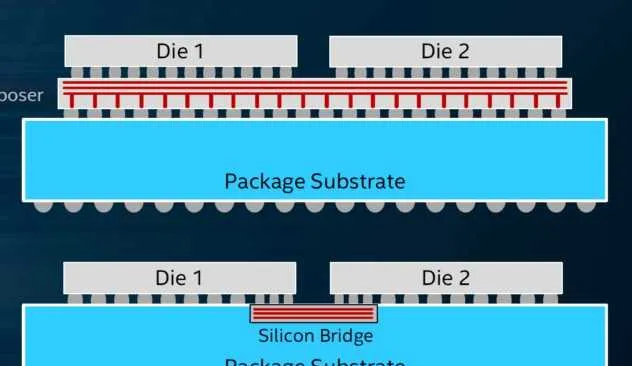

這種做法可以看作業主沒錢搞大平層,但也要這麽多房間,怎麽辦呢?在原地 相鄰得建4個小高層 ,再把小高層連起來,房間數目不變。怎麽把它們連起來呢?比較現代的做法有兩種:

這種做法也叫做MCM(Multi-Chip-Module),詳細內容可以看我的這篇文章:

其中AMD采用矽中介(Interposer),也就是上面那種;Intel采用 EMIB(Embedded Multi-die Interconnect Bridge), 是下面那種。

矽中介的做法可以看作為了兩個樓互通,我們把地下都挖空了,搞了個換乘大廳。而EMIB可以看成在兩個樓之間挖了一個地下通道。顯然挖通道更省錢省力,但因為通道是兩兩互聯的,如果大樓多了,還不如換乘大廳方便。

好了,那我們的串門問題怎麽解決呢?因為樓和樓(Die和Die)之間只有地下互通,要串門的人都要做電梯到地下一層,透過地道或者換乘大廳到另一個大樓地下,再做電梯去想要的樓層。路途遙遠,好多人都不想串門了,同時如果串門人太多,會擠爆電梯,不得不串門聯系工作的人們在電梯口排起了長隊。顯然,建築四個相鄰小高層的辦法,延遲和頻寬都比較差。

那麽多CPU呢?

還是沒錢蓋大平層,這次更慘,因為4層小高層間隔比較遠,為了方便人們串門,不得不在園區裏面搞了班車,用於跨樓通勤。因為班車開停需要時間,人們串門更加麻煩了。

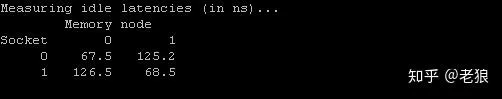

借助這個比喻,我們應該能夠得出結論,這三種方式提供48核的算力,延遲和頻寬是依次下降的。下降的振幅和需要進行的work load有關,不能一概而論。大家可以借助一個工具 [1] 來具體測量一下記憶體的延遲:

在這個例子裏面看出,本大樓的存取延遲比跨大樓的存取延遲低了一倍!

成本差距

既然大平層這麽好,為什麽還有人蓋小高層呢?存在都是合理的,當然是成本高了。我在這篇文章中講述了為什麽Die大了成本就高:

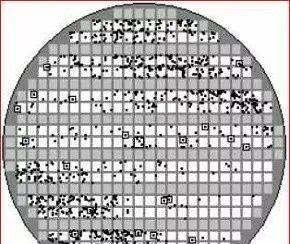

簡單來說,晶圓在制造過程中總是避免不了缺陷,這些缺陷就像撒芝麻粒,分布在整個Wafer上:

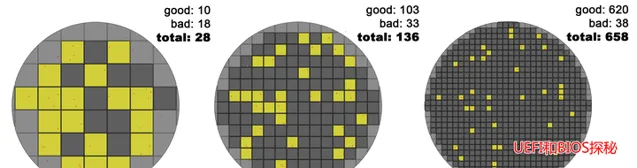

如果考慮缺陷,Die的大小會嚴重影響良率:

上圖大家可以點開看(圖比較大),其中不太清楚的紅色小點是晶圓的缺陷,在Die很大時,有很大概率它的範圍內會缺陷,而只要有缺陷該Die就報廢了(簡化處理);在Die比較小的時候,它含有缺陷的可能性就大大降低了。如圖中,隨著Die的減小,良率從第一個的35.7%提高到了95.2%!我們舉個極端的例子,整個Wafer就一個Die,那麽良率只有0%了,生產一個報廢一個。誰還幹這麽傻的事!

這種成本增加不是線性的,而是指數性增加,具體的數碼是廠商的核心機密,不為外人道。但總的來說,結合前面的例子來說就是:

1個大Die成本 > 4個小Die+互聯路線總成本

那麽方式2和方式3成本誰高呢?實際上方式2節約了主機板上大量布線和VR等成本,總成本更低,也是主機板和伺服器廠商喜聞樂見的形式;而方式3往往用於堆出更多的內核和需要更多記憶體的情況。

結論

相信讀到這裏,同學們已經有了答案,結論開頭已經說明,就不再贅述了。多核CPU和多Die乃至多路CPU,對作業系統等來看,區別不大,BIOS都報告了同樣多的很多CPU供他們排程。區別主要在於效能上面,大Die多核效能最好,也最貴。多Die效能下降,但經濟實惠。最後要註意,這些效能區別有些是作業系統可以感知的,如透過NUMA等方式:

作業系統可以具體做出最佳化。但也有部份是作業系統不能夠知道的,只有透過各種真實的workload,使用者那裏才會感覺有明顯的不同。

最後推薦11代內核的NUC,很好用

BIOS培訓雲課堂 :

其他CPU硬件文章:

歡迎大家關註我的專欄和用微信掃描下方二維碼加入微信公眾號"UEFIBlog",在那裏有最新的文章。

參考

- ^ Intel Performance Checker https://software.intel.com/en-us/articles/intelr-memory-latency-checker