這個極限遠大於題主所說的0.5nm。

半導體廠的節點命名已經和實際器件尺寸脫節了,節點名比如7nm似乎不代表芯片上某處的特征尺寸。依我所學,對於ASIC/DRAM來說,節點名應當是第一層金屬層M1層的 half-pitch,但實際上看起來並沒有聯系。這裏希望有做工藝的人解釋一下當前這些節點都是怎麽定義的。

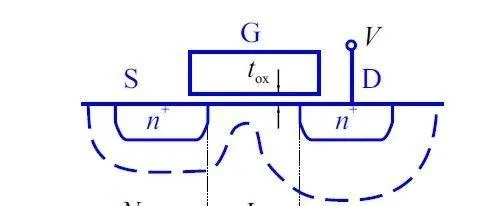

但,金屬氧化物場效應管(MOSFET)的溝道長度 L 是有極限的,就是MOSFET的柵極下從源(Source)到漏(Drain)的一段長度。

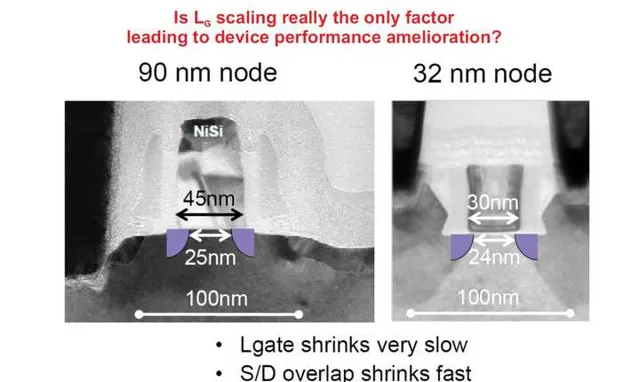

下圖是MOSFET在掃描電鏡SEM下的剖面圖。90nm節點下溝道長度是25nm,但是32nm節點下溝道長度只縮小了1nm。溝道長度的微縮非常緩慢。溝道長度牽扯到的電學效能變化就太大了。這裏只說說S/D量子穿隧的問題。

這個長度L小於8nm後一般認為MOSFET的開關功能就廢了。因為電子的熱德布羅意波長(Thermal De Broglie wavelength) \lambda_{th} 在常溫下就在幾nm這個數量級。熱德布羅意波長公式如下 [1] ,可以自行帶入數值算算:

\lambda_{th} = \sqrt{\frac{2\pi \hbar^2}{mk_B T}}

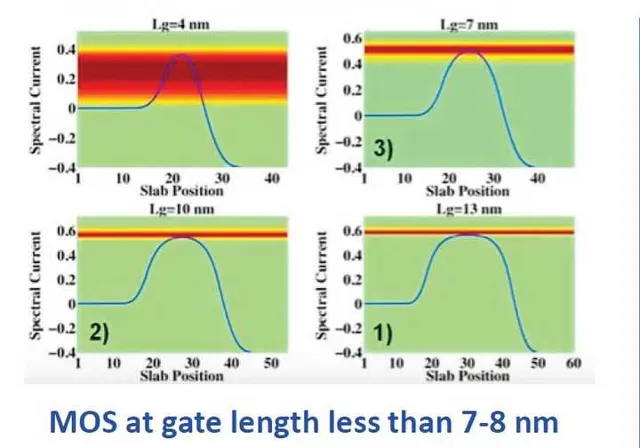

如果溝道長度 L 就在7-8nm這個數量級的話,大量電子在常溫下輕松依靠量子穿隧效應透過勢能壁壘從Source直接到達Drain。宏觀上看就是晶體管沒有關閉(Off)狀態。如果ON/OFF的電流比值沒法達到一定閾值的話,邏輯0和1是不好區分的,對於高效能(High performance)芯片的工藝這個ON/OFF電流的比值大概在 10^4 左右。這個問題就是Source-drain tunnelling,晶體管尺寸的最終極限,受制於量子力學定律。一些基於量子力學的電子運輸(Quantum transport)計算的方法比如非平衡態格林函數(NEGF),可以給出溝道電流的能量分布,這部份需要量子場論的知識就不多談了(場論真的不懂)。在經典物理框架下,電流只能由能量高於勢壘(Potential barrier)的載流子貢獻,效果如下圖中溝道長度為13nm的(右下圖),量子效應微弱幾乎不顯現。但是溝道度在7nm左右時,量子效應開始顯現,在勢壘比較窄的頂端有一部份載流子在能量沒有高於勢壘的情況下也透過了勢壘,使得總電流大於經典框架下計算到的電流。這時候器件效能就很差了,在實際中已經失效。MOS場效應管要關閉就靠這個勢壘能調控溝道的電流大小。如果在4nm(左上圖)可以很明顯看到,勢壘完全不能阻擋電流的流過,最終柵極對溝道的調制功能完全失效,根本沒有OFF狀態。

這裏討論的量子效應並不是已經顯著發生在今天芯片中造成Gate leakage的量子效應。那個是電子依靠量子穿隧穿過了柵氧化層,已經在更早的節點中就顯現了,解決辦法就是用高K材料做柵極氧化層,在保持等效氧化層厚度的時候增加了氧化層的物理厚度,削弱量子效應。

但是台積電依舊可以往下開發新的節點名,7nm下來5nm,再下來3nm,2nm....畢竟數碼不斷的演進帶來了技術持續飛躍的直觀感覺。但是溝道長度還能再微縮多少,這是個問題。當今芯片還有高密度整合帶來的散熱難題,互聯層難以微縮以及銅互聯的高延遲問題等等。摩爾定律要續命今後將越來越依賴於架構(Architecture)方面的改進。

參考

- ^ 來源於維基百科 https://en.wikipedia.org/wiki/Thermal_de_Broglie_wavelength