寫這個主要是為了完成作業,領導轉發了夏core的文章,其中,特別對 第四招:GPGPU相比DSA對AI天生不足 ,領導們想知道裏面說的有沒有道理,以及針對這些觀點,我們的看法是什麽。於是,周末展開寫了一些自己的觀點。

附原文:

時間有限,只接第四招!

GPGPU是AI最高效的計算硬件架構嗎?

「很明顯的答案,不是。」

我也贊同!

雖然答案相同,但理由不同:GPGPU只是一個名詞,代表通用計算為目的芯片,不是固定的架構。不同家的GPGPU,雖然都是叫GPGPU,其實架構差別很大的;而Nvidia十幾年前的GPGPU和現在的Hopper架構,差別也是非常大。

既然GPGPU不是特指一個固定的硬件架構,那討論它是不是AI最高效的計算硬件架構,是沒有意義的。它適合在CPU/GPU這個更高維度來做區分對比。

相關專業從業者,要做AI架構比較的時候,最好直接拿兩個架構對比,比如NV Hopper vs. Google TPU v4;NV Grace-Hopper vs. Tenstorrent Grendel。

PK完了之後,看看誰勝出。誰就當下AI最高效的計算( 硬件 )架構。(最好去掉硬件,單獨討論硬件好像沒什麽意義。)

GPGPU相比DSA對AI天生不足嗎?

芯片架構都是「人」生的,沒有「天」生的!

「不」足是可以「補」足的!

在Graphcis+AI芯片行業工作馬上二十年了。我經歷過幾次非常大的硬件架構升級,軟件架構重構,推翻重寫。每次都是以年為時間單位的大專案。升級/重構是非常辛苦的事,但這些都是為了活提供更好的特性,或解決客戶的痛點,不做公司就得死。

不得不承認,Nvidia在變革這一方面,經常是引領者!所以我並不懷疑他們對自己不足點的感知能力,以及他們的糾錯補足能力。不論在AI計算的 最前沿 :大學,研究機構的演算法研究中;還是在工業界 最廣泛 的各個領域的AI計算實際套用中,都有大批的NV工程師,架構師去對接,獲取第一手的反饋。最終將合適的架構改動反映在芯片架構中。

比如,我們只看到Hopper在Transformer引擎加持下跑大模型效能爆表,仔細反推一下,Nvidia的架構師們在2019/2020年就已經感知Transformer演算法在未來AI計算的重要性,然後做架構方案,實作在Hopper架構中,而當大模型大火之時,一個幾倍效能/能效的Hopper架構真的是讓對手們難以招架。

架構服務於需求!有需求就改架構!

從GPU到GPGPU,是從Graphics到通用計算的的一個(DSA -> General)的過程。

現在AI有超大需求,反過來,再從GPGPU演進到一個GP-AI-PU,甚至AI-PU,也沒什麽不可以的。

Nvidia透過在SIMT架構的緊耦合擴充套件, SIMT本身的架構會約束限制了其AI DSA的上限?

大家對SIMT技術有些誤解。

SIMT,就其字面含義,Single Instruction Multiple Threads,只是GPGPU在微架構層次(Warp/Thread)上的一個技術架構,因為涉及到指令集和編程模型,給使用者帶了很多便捷,所以名聲比較大。但把它和GPGPU架構放在一個級別,甚至畫上等號,這是一個概念上的錯誤。

它真的只是整個架構裏非常非常小的一個技術,局限在SM核內很小的一部份管理warp內執行緒的微架構,對AI計算的Pattern(模式)來說,它的重要性比較低。因為AI算子中,需要精細branch控制的部份很少。

對於大型AI計算,NV的架構中,是采取多層次(Hierarchy),分而治之的策略。它在每一個層次上,都有很多相關的技術。下面,1-5是單芯片內的層次,6-8是多芯片scale-out:

- Thread:對一個warp內的threads(x32)進行管理,SIMT,Predicate,EMask,...

- Warp:對一個PU內的多個warp(x8/16)進行管理,Warp Scheduler,Multi-issue,...

- Block:一個SM內有多個PU(x4),它們之間需要block級別的管理,任務的顆粒

- Cluster:一個Cluster內多個SM(x16)協作管理,合作完成一些需要較大SRAM(MB大小Shared Memory)的任務,

- Grid/Device:100多個SM的管理,

- Grace-Hopper:CPU-GPGPU之間NVLink-C2C,插一句,NVlink C2C相容CXL。

- NVLink:節點內多GPU連線,

- NVLink-Switch:多節點連線

有機會對多層次(Hierarchy)計算架構,和其它扁平式(層次較少)的DSA架構做一些對比分析。一個合適的架構層次對計算的控制流,數據流,軟件的復雜度等關鍵指標影響很大,值得詳細分析。

DSA on Hopper

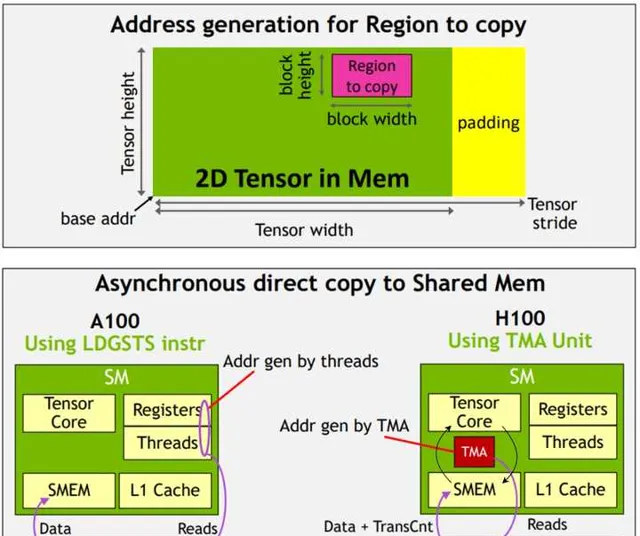

拋開Transformer引擎,Hopper架構在Block/Cluster這兩個層次,增加了不少新特性,基於這些新特性,打造了一個脫離SIMT(threads)的編程模型和指令集,能完成一套完全等於普通DSA的Buffer+DMA結構的編程和計算控制。在整個conv/matmul的編程中,甚至不需要任何的vector/SIMT相關的指令。

夏Core舉例說的SIMT/Tensor core,其實還停留在老的架構的理解上,這裏可以對Hopper幾個特性做一些簡單介紹,其實NV對AI的DSA化支持力度其實很大了。

簡單的說,Hopper架構的DSA改進,和SIMT沒關系,也不會受到SIMT的限制。

相關DSA特性包括

其中,TMA支持img2col,multicast,shared memory swizzle等;

Async warpgroup-level MMA:包括大size(64×32B×256)的MMA,直接讀寫shared memory,SM內所有Tensor core協同工作機制。算力也和壁仞的一個CU(4個Tcore/PU)的差不多。這裏有一些介紹,大家可以看一看:

而後面兩個特性(DSMEM+Async barrier),更是能將Cluster裏多個SM協同完成更大的conv/matmul,減少外部頻寬需求。當然合作方式並不是壁仞的脈動方式,而是各自獨立,但支持DSMEM存取,數據廣播,優點是更靈活,算力更大!缺點是復雜度比較高。

基本上, 上面特性完全解決了原文中提到的數據通路和Tensor Core尺寸的問題。

而且,不考慮量化等Fused操作的話,整個Conv/Matmul類別的算子裏,你都看不到任何thread概念的程式碼/指令,完全就是基於tile的Tensor+DSA編程模式。

其它

以後有機會,再探討探討其它幾個話題:虛擬化,CPU-GPU融合,統一記憶體架構和編程模型等。

不可否認傳統的GPU/GPGPU都有其歷史包袱。但並沒有阻止大家努力地把架構往新的方向推動。比如十幾年,AMD(前司)的Phil Rogers就在大力推行HSA,另一個前司(ARM),當時Jem Davies也是大力輔助。可惜還是沒有成功。現在ARM在Mobile上推了幾年的Total Computing。總之,新技術的推廣落地確實很難。很多技術都是好技術,技術的支持確參雜太多利益,這是一些公司/組織推動技術和規範時總遇到的問題。回過頭來看,NV在這一塊其實做得還挺成功。

交作業。夏core刀下留情!