嗯… 沒人邀… 湊一發熱鬧。

有謬誤歡迎指正, 非核工程專業.

非常大。

電路是靠著電容上積累的電荷確定0或者1的

電路是靠著電容上積累的電荷確定0或者1的

電路是靠著電容上積累的電荷確定0或者1的

任何形式的放射線, 都會傷害無保護的ASIC電路。 方式多種多樣, 最終目的無非一個: 以游離, 撞擊等方式, 導致Soft Error (軟錯誤, 也即可以糾正的, 不影響硬體本身的錯誤), 其中 single event effect(SEE, 單事件錯誤)是這裏面主要的參量 。嚴重的, 甚至會導致硬體本身損壞(Hard Error ), 也即不可修復的錯誤. 這一點放到後面講.

也就是說, 我往記憶體裏存了個數, 二進制 0000 1111; 結果粒子一打過來,喲呵~ 變成

0001 0111了。

如果是數學運算,… 加減法做不對會導致計算軌域錯誤啊之類的; 如果是控制位… 那你最好保證反轉的那兩個位元沒有控制什麽飛船彈射之類的參數。 不然本來輸入0不要彈射, 一反轉變成1趕緊彈射。玩兒脫了…

比如說車諾比事件之後, 蘇聯令人發指的召集誌願者去清理放射線, 原因是 機器人進去就不聽使喚了. 更嚴重的是, 這些機器人拿出來以後, 也不能使用了.

------------偏題開始-----------

那麽怎麽知道我這個電路會不會這樣呢? 標準方法叫做 SEE testing, 單次事件測試。

這個測試簡單粗暴: 用一束已知能量的粒子去轟擊測試芯片, 同時進行外部操作, 看最終結果會不會翻轉。這一束粒子可以是任何粒子, 包括alpha射線, beta射線, 中字束, 混合各種各樣的粒子等等. 粒子束的強度統一以入射粒子的能量, linear energy transfer, LET來記。具體到數量級上的話, 如果是目前普通的家用電腦,大概游離輻射量 在 0.x keV cm2 /mg 就掛了。 (掛了=出現了軟體諸如 ECC 無法修復的錯誤)

*對於Gamma射線, LET的計算方式不太一樣, 因為這貨是光子; 計算的時候一般是算由Gamma射線引發的電子束強度.

太空的標準參考LET是 60-120 MeV cm2 /mg

垮了噻… 差了幾個數量級啊!

原因是家裏面的電腦由於地球母親磁場和大氣層的保護, 基本不會受到轟擊。 設計的時候, 設計師們都表示呵呵呵呵誰要管你。

太空工程師表示瓦日你哥… 我們怎麽辦…

說一下LET是如何用來測量的: 一般來說, 用一束粒子轟擊這個芯片, 如果這個轟擊有效 (改變了某些元器件電容上的電荷), 那麽這個芯片上會向外射出粒子.

LET, 顧名思義, 線性 能量 轉移, 就指的是在這個有效轟擊裏, 有多少能量被轉移出來了.

LET_thresh, 是對於一個器件來說, 不斷地給它施加高能粒子束, 高到某一個能階的時候, 飛出來的粒子能量不再提升了.

那麽一般來說, 家用機LET_thresh非常低, 表現形式就是稍稍拿粒子轟擊一下, 就會飛出來一堆電子; 但是如果我逐步加大這個粒子束的強度, 出來的電子不會變多!

什麽意思呢? 就是說: 家用機無論你怎麽轟擊, 就只能出來這麽多電子了. 再多的電子在原子內層, 你轟不出來.

為什麽這是一個壞事呢? 半導體裏面可用的電子密度就那麽點點, 結果一點點粒子束就全把它轟出來了剩下的原子核和內層電子等著結婚咩...

所以說, 環境裏面的LET越高, 說明 這個環境有能力轟出更多的電子; 而 器件的LET_thresh越高, 說明這個器件能承受被轟出更多的電子, 也即在高放射線下更加穩定.

在CMOS出生的同時, 太空/核 工程師們就找到了一種能讓標準CMOS 承受高放射線的方法:

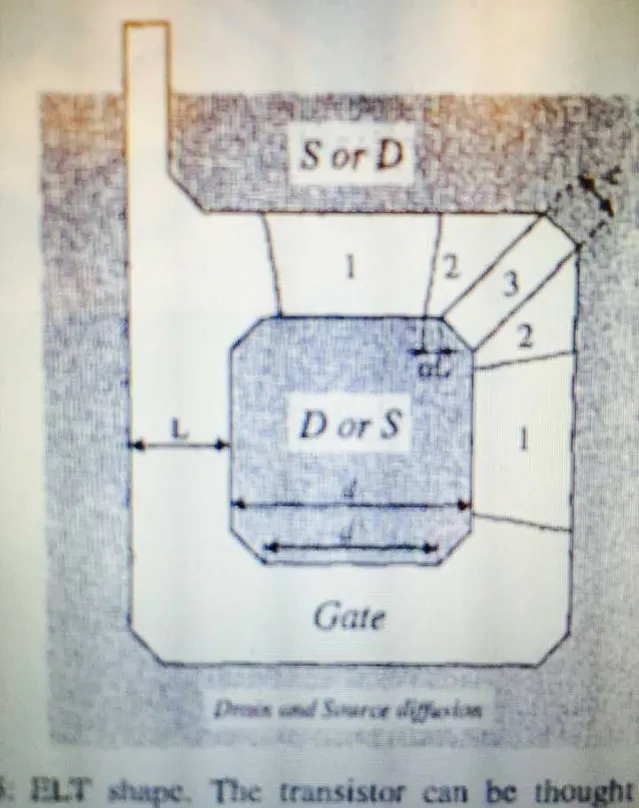

把CMOS設計成這樣:

這叫做 enclosed layout transistor。 很惡心吧! 這玩意兒的 長寬比不再可以簡單的算出來了, 而是要用一套復雜的公式計算。

這樣可以把微米級別的電子芯片做到幾十MeV cm2/ mg。看起來不錯哦~

(該技術依然廣泛套用於目前的航天/高能物理場所)。

但是! 地上的工程師們呵呵一笑: 我們的 sub-micron technology要不要? 要不要? 不要的話我們就繼續奔向奈米級別了, 你們微米級別慢慢玩~~

太空工程師一計算, 0.25um 的 CMOS 只能承受 大概 15MeV cm2 / mg… 表示不開心。

然後, 在CERN 制作 LHC的時候, 又繼續發揚光大, 縮小器件的同時,加入了harden mode(也即在上面那個ELT的基礎上在外圈再加入一圈兇殘的guardring, 這樣可以抵禦相對強烈的粒子束轟擊)

然後就做到了89MeV cm2 / mg, 反正CERN 表示我們的LHC夠用了。

記得太空裏是60-120 MeV cm2 /mg吧… 太空工程師欲哭無淚… 你們做這個才剛剛達標啊!

(原話: 那沒辦法啦… 硬體差不多到頭了…剩下的只能靠軟體了…)

改為: 電路方法克服這些錯誤 基本到頭了, 剩下的靠遮蔽+架構來解決.

克服Soft Error 有兩個無堅不摧的法寶: 把電路做大或者頻率減低. 但是這兩個都會拖慢電腦的效率.

架構上的方式, 基本可以總結為: 加冗余, 交織設計, 和家用機裏也會有的ECC(Error Correct Code). 當然這裏的ECC會不同. (感謝

太初有為的指正! )

加冗余就是把本來一個電路能完成的份額用三個或者更多個(奇數個)電路做, 做出來之後取多數答案當做正確答案. 假設本來某個粒子有50%的可能會翻轉一個位元, 三份冗余之後, 就只有50% * 50%= 25% 的機率了. 另外, 據

太初有為說以及查證, 標準的三份冗余會使用不同的時鐘等, 這樣更是降低了一個粒子幹擾一片電路的可能性.

交織設計在

太初有為的答案裏有詳細的介紹.不再贅述.

參照:

F.Sturesson , TEC-QEC, 「Single Event Effect (SEE) Testing」, EPFL Space Center 9 th Conference., June 2009.[Presentation Slides]

Wikipedia, 「Linear Energy Transfer (LET)」., 2012, obtained : Linear energy transfer .

F. Faccio, K. Kloukinas, A. Marchioro, T. Calin, J. Cosculluela, M. Nicolaidis and R. Velazco, CERN and TIMA/INPG Laboratory, 「Single Event Effects in Static and Dynamic Registers in a 0.25pm CMOS Technology」., IEEE TRANSACTIONS ON NUCI.EAR SCIENCE, VOL 46, NO 6, DECEMBER 1999

G. Anelli, M. Campbell, M. Delmastro, F. Faccio, S. Florist, A. Giraldo, E. Heijne, P. Jarron, K. Kloukinas, A. Marchioro, P. Moreira and W. Snoeys, CERN and University of Padova & INVN, 「Radiation Tolerant VLSI Circuits in Standard Deep Submicron CMOS Technologies for the LHC Experiments: Practical Design Aspects」., IEEE TRANSACTIONS ON NUCLEAR SCIENCE, VOL. 46, NO 6, DECEMBER 1999