作為一個電路設計師,我整個職業生涯都花在介面電路上,序列並列都做過,且速度不慢(DDR3-1600Mbps, SerDes 30Gbps),這個問題不答實在技癢難耐。已經看到的答案中,大家基本上都命中了關鍵的知識點,但是沒有把背後的邏輯說清楚,也沒有人從電學特性和經濟的角度分析這個問題。大言不慚,歡迎大家拍磚討論。

----------2月3日補充--------

名詞解釋:

Mbps, Gbps: 一百萬位元每秒,十億位元每秒

skew:時間偏差,A比B快/慢一秒,就叫skew一秒

PCB:印刷電路板,也就是大多數電路板

IO: 輸入輸出電路

cable: 線纜

SerDes:序列轉並列,並列轉序列

還有人說貫口最快的,我們來算一算。 業界目前大量套用的28Gbps SerDes,傳一個位元只要35.7皮秒,這點時間光在真空中可以走上一厘米,連角膜到視網膜都不夠。 哪個快?

----------正式答案的分割線--------

先說我的答案, 串列埠為啥比並 行接 口快?是因為串口的特性和套用場景,決定了它更加適合采用一些提高單根通道速率的設計方法,這些方法用在並口上並不合適。

討論這個問題,首先要搞清楚定義,什麽叫並列介面(parallel link)? 什麽叫串列埠(serial link)?這就可以吵一天。

並口代表DDR說:「我是並口的純正血統傑出代表,每8bit要附帶一對DQS線作為時鐘,每個bit都要同步到這對DQS上去,skew超標就不能工作,64位元DDR3-1600總頻寬可以到100Gbps,哪個串口做得到」?鄙人冷笑,說:「別以為我不知道你的底細,別看你IO是1.6G,記憶體控制器給你的一般都是4位元並列的400M,你要先悄悄做一下並列轉序列,再輸出。何況你傳64bit數據需要80根全速率的DQ/DQS線,還要20多根半速率命令地址線,平均下來一根線1G還不到」。XAUI舉手問:「我算串口麽?XAUI一定是8組16根差分線,4組讀4組寫,缺任何一組都不符合協定,看著很並列啊?」 32位元的PCI-E也一臉關心的等著答案。

我們先這麽定義 :在 一個獨立的通道上 , 每次同時傳輸1bit為串口,每次同時傳輸多個bit為並口 。標準的串口如XAUI,HDMI等,每對差分線組成一個通道(channel),每個通道是否能成功傳輸並不取決於其他通道。而DDR這種,10根線組成一個通道,每次同時傳8bit,錯了某一bit只能重新傳,便是標準並口,芯片內部的並轉串和IO並不相關,不影響定性。按照這個定義,大家看看各種介面協定怎麽劃分呢?我覺得已經很清楚了,以單個channel的傳輸速率衡量,串口一般來說更快。下一個問題就是,為什麽呢?

這是一個電學問題,但首先是一個經濟問題。

對任何一種協定,提高總頻寬不過是兩種辦法,首先要提高單根線的傳輸速率,其次只能增加電線的數目。增加線的數目實在費錢,首先現在的芯片往往IO都很緊張,增加了IO PAD還要搭上額外的ESD和面積;封裝和PCB上增加額外的線更復雜更貴這就不用說了,對於某些用cable的協定基本就是不可接受的。你是願意插16根網線還是一根?接電視機的時候喜歡一根線的HDMI,還是五根線的RGB+音訊?還有

@Arthur Wang提到的150米長線。。。。。。何況並口還要對這些線進行長度匹配,想想頭就大了。

歷史上,工程師們確實是先做了串口,速度不夠沒辦法只好含淚加電線上並口,直到他們發現了三大法寶來提速,並口的動力就不那麽強勁了,正如

@auxten所言。但是在芯片內部,增加總線寬度的代價並不高,因此CPU裏面有個1024位元的數據總線也不奇怪。

為了提高單根線的傳輸速率,必須要講到我們模擬電路工程師的三大法寶, 差分訊號(differential signaling),時鐘-數據恢復(Clock-Data Recovery,簡稱CDR),和通道均一化(Channel Equalization,Eq)。

差分訊號 的好處

@龔黎明@andrew song已經提過了,不外乎抗幹擾能力強,引入的雜訊也比較小,雖然必須要兩根線,但速度從幾百M提高到幾G,還是很值得的。

CDR的好處

@龔黎明也說過了,消滅了skew,減少了時鐘的功耗和雜訊(但多出了CDR電路本身的功耗和雜訊),同時避免了電磁幹擾。想想在PCB或者電線上傳一個15G的時鐘,太帶感了,幸虧我們不用做這種事。

通道均一化 相當值得一提,這才是SerDes高速發展的決定性因素,所以我決定花點文字講一下。

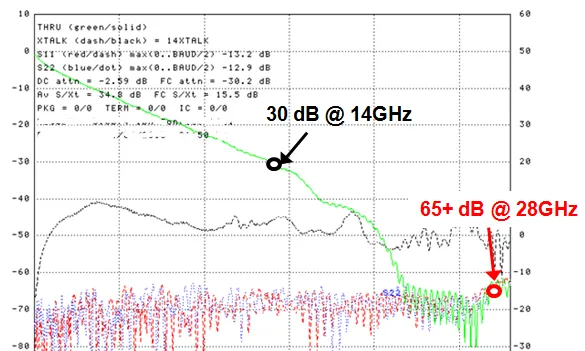

一般來說,真實世界中的通道都是低通特性的,到處都是小電容,所謂絕緣體中的分子在高頻情況下吸收電場能量,再加上金屬線中的趨膚效應,所以我們想要的高頻訊號走不了多遠就不像樣子了,比如下面某通道的頻率特性(綠線)。

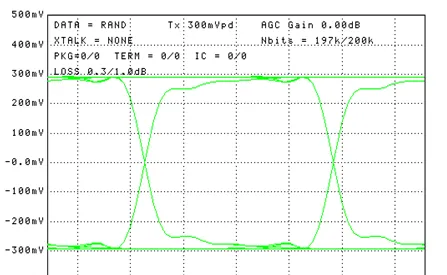

如圖所示,在對應28Gbps的頻點上,訊號能量被衰減了30db,電壓振幅只剩3%了;在對應56Gbps的頻點上更慘,65db意味著訊號電壓擺幅剩下不到千分之一。在這種通道中,發送端一個完美漂亮的數據眼圖:

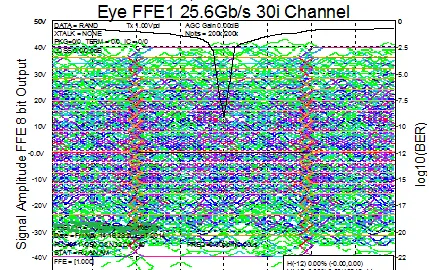

到了接收端會變成這樣的一堆垃圾:

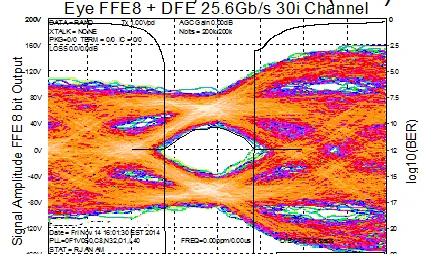

什麽都辨認不出來對吧。但是,經過我們聰明的工程師們一番努力,均一化開關開啟,訊號就變成了這樣:

神奇麽?我覺得挺神奇的,我認識的電子工程師們第一次看到這個,沒人覺得不神奇。

下面一個重要的問題,既然有了三大法寶,他們只能用在串口上嗎?

答案很顯然,不是,串口可以用的,我們並口一樣可以用。那為什麽並口不用呢?

差分訊號 這條不用說了,並口的電線本來已經夠多了,數目還要再翻一倍?系統工程師會殺人的。

CDR 意義也不大,反正你並口速度也不高,一堆數據線中順便傳下時鐘,比做接收端做CDR再采樣每一位數據省事多了。

通道均一化 屬於屠龍之技,不用差分訊號的話也就傳幾百M,本來就沒啥衰減,用這個幹啥?還是考慮下各種雜訊串擾的問題吧。

於是答案就呼之欲出了。 串口為啥比並口快?是因為串口的特性和套用場景,決定了它更加適合采用一些可以提高單根通道速率的設計方法,這些方法用在並口上並不合適。

從現有的套用看來,需要持續穩定高頻寬的套用,往往使用高速串列埠,一根頻寬不夠再加一根,各種影片網絡套用,基本如此。而一些歷史遺留速度不高的套用,還有一些需要突發性高頻寬的套用,並口仍然存活,比如很特殊的DDR。雖然XDR/GDDR/HMC/HCM這些新標準都在試圖引入SerDes, 但DRAM行業的特殊性還是讓並口繼續存活著。

最後一段是我對

@龔黎明答案的批評,歡迎指正。這個答案清楚明晰的指出了幾乎所有串口的優勢,但是忘了提及一點,這些優勢其實是三大法寶帶來的,並非串口與生俱來。就像小強開車小明走路,小強自然快很多,但並非他天生就快,而是因為小明腿短夠不到油門。蛤蛤蛤蛤