这个极限远大于题主所说的0.5nm。

半导体厂的节点命名已经和实际器件尺寸脱节了,节点名比如7nm似乎不代表芯片上某处的特征尺寸。依我所学,对于ASIC/DRAM来说,节点名应当是第一层金属层M1层的 half-pitch,但实际上看起来并没有联系。这里希望有做工艺的人解释一下当前这些节点都是怎么定义的。

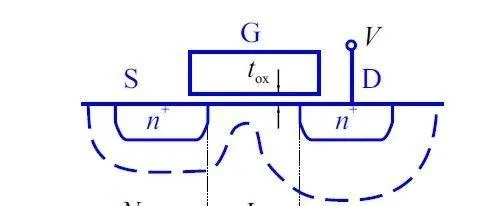

但,金属氧化物场效应管(MOSFET)的沟道长度 L 是有极限的,就是MOSFET的栅极下从源(Source)到漏(Drain)的一段长度。

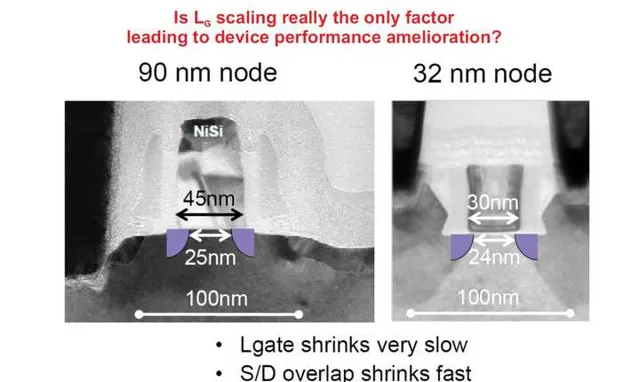

下图是MOSFET在扫描电镜SEM下的剖面图。90nm节点下沟道长度是25nm,但是32nm节点下沟道长度只缩小了1nm。沟道长度的微缩非常缓慢。沟道长度牵扯到的电学性能变化就太大了。这里只说说S/D量子隧穿的问题。

这个长度L小于8nm后一般认为MOSFET的开关功能就废了。因为电子的热德布罗意波长(Thermal De Broglie wavelength) \lambda_{th} 在常温下就在几nm这个数量级。热德布罗意波长公式如下 [1] ,可以自行带入数值算算:

\lambda_{th} = \sqrt{\frac{2\pi \hbar^2}{mk_B T}}

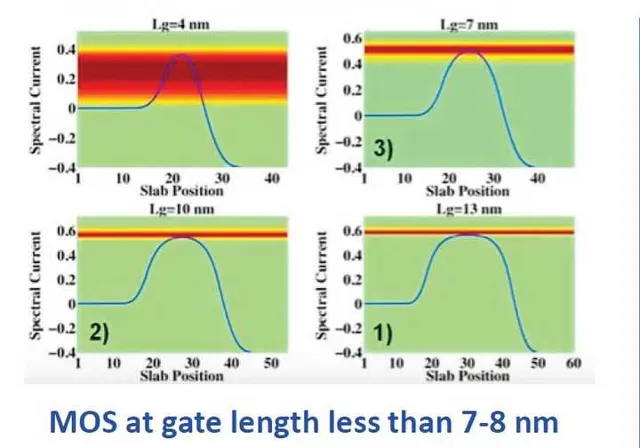

如果沟道长度 L 就在7-8nm这个数量级的话,大量电子在常温下轻松依靠量子隧穿效应通过势能壁垒从Source直接到达Drain。宏观上看就是晶体管没有关闭(Off)状态。如果ON/OFF的电流比值没法达到一定阈值的话,逻辑0和1是不好区分的,对于高性能(High performance)芯片的工艺这个ON/OFF电流的比值大概在 10^4 左右。这个问题就是Source-drain tunnelling,晶体管尺寸的最终极限,受制于量子力学定律。一些基于量子力学的电子运输(Quantum transport)计算的方法比如非平衡态格林函数(NEGF),可以给出沟道电流的能量分布,这部分需要量子场论的知识就不多谈了(场论真的不懂)。在经典物理框架下,电流只能由能量高于势垒(Potential barrier)的载流子贡献,效果如下图中沟道长度为13nm的(右下图),量子效应微弱几乎不显现。但是沟道度在7nm左右时,量子效应开始显现,在势垒比较窄的顶端有一部分载流子在能量没有高于势垒的情况下也通过了势垒,使得总电流大于经典框架下计算到的电流。这时候器件性能就很差了,在实际中已经失效。MOS场效应管要关闭就靠这个势垒能调控沟道的电流大小。如果在4nm(左上图)可以很明显看到,势垒完全不能阻挡电流的流过,最终栅极对沟道的调制功能完全失效,根本没有OFF状态。

这里讨论的量子效应并不是已经显著发生在今天芯片中造成Gate leakage的量子效应。那个是电子依靠量子隧穿穿过了栅氧化层,已经在更早的节点中就显现了,解决办法就是用高K材料做栅极氧化层,在保持等效氧化层厚度的时候增加了氧化层的物理厚度,削弱量子效应。

但是台积电依旧可以往下开发新的节点名,7nm下来5nm,再下来3nm,2nm....毕竟数字不断的演进带来了技术持续飞跃的直观感觉。但是沟道长度还能再微缩多少,这是个问题。当今芯片还有高密度集成带来的散热难题,互联层难以微缩以及铜互联的高延迟问题等等。摩尔定律要续命今后将越来越依赖于架构(Architecture)方面的改进。

参考

- ^ 来源于维基百科 https://en.wikipedia.org/wiki/Thermal_de_Broglie_wavelength