發一個老段子:馬屁股決定太空梭火箭助推器的寬度

現代鐵路兩條鐵軌之間的標準距離是四英尺又八點五英寸。原來,早期的鐵路是由建電車的人所設計的,而四英尺又八點五英寸正是電車所用的輪距標準。

那麽,電車的標準又是從哪裏來的呢?

最先造電車的人以前是造馬車的,所以電車的標準是沿用馬車的輪距標準。

馬車又為什麽要用這個輪距標準呢?英國馬路轍跡的寬度是四英尺又八點五英寸,所以,如果馬車用其他輪距,它的輪子很快會在英國的老路上撞壞。這些轍跡又是從何而來的呢?從古羅馬人那裏來的。因為 包括英國的長途老路都是由羅馬人為它的軍隊所鋪設的,而四英尺又八點五英寸正是羅馬戰車的 任何其他輪寬的戰車在這些路上行駛的話,輪子的壽命都不會很長。

可以再問,羅馬人為什麽以四英尺又八點五英寸為戰車的輪距寬度呢?

原因很簡單,這是牽引一輛戰車的兩匹馬屁股的寬度。

故事到此還沒有結束。美國太空梭燃料箱的兩旁有兩個火箭推進器,因為這些推進器造好之後要用 路上又要透過一些隧道,而這些隧道的寬度只比火車軌域寬一點,因此火箭助推器的寬度是由鐵軌的寬度所決定的。

所以,最後的結論是:「路徑依賴」導致了美國太空梭火箭助推器的寬度,而這個寬度竟然是兩千年前由兩匹馬屁股的寬度決定的。

一旦人們做了某種判斷,就好比走上了一條不歸之路,慣性的力量會使這一選擇不斷自我強化,並讓你輕易走不出去,這種現象就被稱為「路徑依賴」。

------------------------------------------------------------------------------------------------

對於各種高速序列訊號來講,也有同樣的「路徑依賴」,源頭是從哪裏開始的,這個說不清楚了,我個人認為一個源頭就是數據傳輸。

上世紀七八十年代就出來了各種數據傳輸的協定,比如T1/E1載波系統(2.048Mbps)、X.25中繼系統、ISDN(綜合業務數位網)等,那時的速度還比較慢的,到了九十年代,SDH(Synchronous Digital Hierarchy,同步數位體系)和SONET(Synchronous Optical Network同步光纖網)標準出現,其基本速度就是STM-1 155.520Mbps,STM-4為622.080Mbps,STM-16為2488.240Mbps,到更後來WDM(Wavelength Division Multiplexing, 波長分波多工)技術,再到最新的OTN(OpticalTransportNetwork,光傳送網),這裏面最重要的個概念就是TDM(Time Division Multiplexing, 分時多工)。

分時多路復用 ( Time-Division Multiplexing,TDM )是一種數位的或者模擬(較罕見)的多路復用技術。使用這種技術,兩個以上的

訊號或數據流可以同時在一條通訊路線上傳輸,其表現為同一通訊通道的子通道。但在

物理上來看,訊號還是輪流占用物理通道的。時間域被分成

周期迴圈的一些小段,每段時間長度是固定的,每個時段用來傳輸一個子通道。例如子通道1的采樣,可能是

字節或者是

數據塊,使用時間段1,子通道2使用時間段2,等等。一個TDM的幀包含了一個子通道的一個時間段,當最後一個子通道傳輸完畢,這樣的過程將會再重復來傳輸新的幀,也就是下個訊號片段。來源維基百科:

https:// zh.wikipedia.org/wiki/% E6%97%B6分多路复用數位傳輸就像打包裹,最基本單元是一個小包裹,四個小包裹打成一個中的,再四個中的打成一個大的,再四個大的打成一個更大,然後再特大的。比如SONET的傳輸速度就是STM-1/-4/-16等這樣疊加上去,以2的指數倍往上翻。其中TDM-16速度為2488.240MBps,就是我們通常說的2.5Gbps。

上面說了堆協定,那總要具體的物理實作,一般選用銅線或光纜進行遠距離傳輸。以光纜為例,數據先由電路中的並列數據變成序列傳送出去,然後再經過光纖介面,變成光訊號在光纖裏傳輸,接收時先由光訊號變成電訊號,再由序列變成並列到內部使用。其中由並列到序列/序列到並列經過的就稱為SERDES PHY,高速SERDES的技術實作難度較高,得由模擬電路實作,在很多場合就是一塊單獨的SERDES PHY芯片,那就有專門的公司來做這個事情,比如在業界大名鼎鼎的TI德州儀器,其TI芯片就賣得很好。逐漸實作這樣的產業鏈:做數位電路的、模擬電路的、測試裝置的、生產制造的(包括PCB和SERDES PHY、光口、光纖等),已經定了個基本速率後,再往上的更新換代往往是X2地疊加,在數位電路上最好實作,在模擬電路上也有這樣的動力,整個技術就一直這樣往前走下去。

回到標題高速串列埠由什麽決定的來,PCI匯流排由Intel公司於91年提出,之後移交給第三方機構PCI SIG。PCI SIG由多家業內公司組成的聯盟,別的公司也可以申請加入成為會員,TI也是早期會員之一。就像聯合國一樣,Intel等公司像常任理事國一樣擁有更大的主導權;USB於94年由帶頭大哥Intel聯合微軟、HP、NEC等電腦公司組成USB-IF組織,96年推出USB 1.0標準;(同期還有Apple推出的FireWire火線,也紅火了好多年)由此可見,Intel對PCI/PCIE和USB的建立和發展一直擁有極大的主導權。

2001年PCIE開始制定,決定以序列方式代替並列的PCI匯流排時,那時產業內2.5G PHY已經比較成熟了,PCI組織PCI-SIG決定直接借鑒此速度就很正常;等到PCIE 2.0釋出已經是過2007年,就直接X2變成5G了; USB 3.0於2008年釋出,直接借鑒業界比較成熟的5G方案也就很正常了; 而PCIE 3.0釋出是2010年時(為什麽PCIE 3.0是8G而不是10G,這算是個折衷吧,速度越快對PCB走線設計和生產、線纜、測試儀器等要求越高,3.0采用64b/66b或128b/130b編碼方案,8G*64/66=7.88G,解碼後的速度幾乎就是2.0的二倍,2.0采用傳統的8b/10b編碼,解碼後速度5G*8/10=4G)。

等到USB3.1釋出,也就是最近的事情(2014年),覺得10G PHY也比較成熟了,那也直接采用10G吧,USB 3.1采用128b/132b編碼,效率與PCIE 3.0是等效的,它直接向PCIE借鑒了很多內容。

而ThunderBolt,定位在更高速速度傳輸,其1.0速度最開始設計時就是一 路10G PHY(大約2011年),而後2.0就成兩路10G PHY了,最近的3.0成兩路20G PHY,為什麽不直接成40G PHY,工藝做不上去啊。

很早前,業界有個傳說,銅界質PCB走線最高速度只能到16G,幾年前就已經打破了,28G甚至32G以上跑銅界質的高速PHY已經有DEMO演示了,ThunderBolt 2.0推出兩路10G PHY,自然也是業界有這樣能力去推出成熟產品。

不出意外的是,ThunderBolt定位在高端,從最先推出1.0介面的MAC電腦(2011年),到現在已經四年過去了,相對來說還很不普及,只在高端電腦上才有配備,其外設產品,比如支持該介面的外接儲存和高畫質顯視器見到過報道,但市場上賣得真不太多,比起這幾年一下子普及開來的USB 3.0還是相差不少。與此類似待遇的是DisplayPort介面,顯視器介面從最早的VGA到DVI,到同時支持聲音影像傳輸的HDMI、DisplayPort介面,HDMI逐漸變得常見,尤其是電視介面上,而DisplayPort仍然不太多見。而ThunderBolt在外觀上與Mini DP介面相容,在功能上可認為是影像傳輸介面DP和數據傳輸協定PCIE的合體。

這不,Intel一琢磨,那ThunderBolt 3.0改成USB3.1-C介面相容吧,這樣支持ThunderBolt 3.0的外設既可以連線對應的ThunderBolt 3.0 host,享受40G的高速,也可以接在USB3.1-C上,盡管只能跑USB 3.0 5G速率(註意,資料顯示所相容的控制器是USB 3.0,而不是最新的3.1; 也有人指出Intel推出的控制器是支持10G速度的。anyway,PHY通道是支持的,這主要取決於控制器部份),但是更常見啊,這樣對於外設廠商也是一大利好,使用者也可以放心地買啦,不用擔心介面不支持啦。

最後做個總結:高速串列埠速度由什麽決定?當時協定公布時前代技術的積累與影響和已成熟技術,二者占重要因素。比如2.5G速率和STM-1 155M的關系,比如不同年代PHY技術的成熟度,再者還有業界領先公司在制定標準時的號召力及技術前瞻性,如Intel在多種協定上的主導力。

這裏順便吐槽下動不動國產OS、國產某技術、國產CPU……試圖與業界流行的產品和技術對抗,想另起爐竈,而其本質往往只是在人家已有技術的基礎上借鑒人家的思路,抄襲或模仿成類似的產品,尤其是ZF在其中扮演主導角色,這種努力往往失敗,也許在某些不開放場合有一席之地,只要是開放市場,幾乎無競爭力,不提其它,一個路徑依賴就把你拍死了。那些號稱的自主、國產,開發過程和產品裏仍然有大量開放世界裏的工具、成熟產品、思維、架構體系,那做出來的東西只是在某一個細節上對已有產品形成了可替代力,但其上遊、下遊還是與業界緊密聯系在一起,這種情況下很難有所發展。

-------------------------------------------------

前不久還寫了個回答,也一起貼大這裏:

如何看待 Thunderbolt 3 改用 USB-C 介面?手頭正用的是Macbook Pro 2012年版,用的視訊輸出介面是Thunderbolt 1,介面與Mini DisplayPort介面相容,現用HDMI介面外接顯視器,要使用個轉接器。

為什麽Thunderbolt 3要改成USB3.1-C相容介面?因為它是Intel啊,這兩家標準都基本以Intel為主導啊,PHY team的人碰碰頭,小會議室一坐,說咱們做成一樣的吧,就成啦!

從商業角度來講,統一標準有多少好處,Thunderbolt現在流行範圍還不廣泛且由Intel主導,阻力比較小等考慮就不多說啦,談點技術上的實作。

為什麽插上去可以實作相容?因為它們都屬於高速序列傳輸協定,在技術上有很多共用的地方,且在速率上不同的代本身是匹配的(Thunderbolt 1的速度就是10Gbps,與USB3.1一致),再者不同的高速序列協定往往是上層協定不同,在底層實作上是通用的,也就是控制器不同,而PHY可以通用。

我在S公司做過較長時間的PCIE原型平台驗證,主要是數位電路部份的控制器程式碼燒錄到FPGA中,已經流片成功被做過基礎電學測試的PHY測試芯片做成單獨的子卡扣在原型平台上,再與PC主機板連線進行測試。最高支持10Gbps的PHY子卡不僅僅用於PCIE GEN3 8Gbps,同時還支持SATA GEN3 6Gbps和USB3 5Gbps(是否還支持USB3.1 10Gbps還要確認下,按理說支持),子卡上留有多種介面,PCIE金手指、SATA介面、USB介面等,哪個計畫要測試了,直接從一個平台拔下來,換上介面放另一個平台就可。這個過程中,FPGA內的控制器程式碼是變化的,同時上電時會對PHY子卡配置一組向量去支持不同的模式。

並且這些協定不同的代數間往往速率是成倍翻的,不僅是PHY的速率成倍翻,而且控制器內部的執行時鐘或數據位寬也是成倍翻。比如PCIE GEN1 2.5G, GEN2 5G, GEN3 8G(編碼方式從之前的8b/10b變成64b/66b或128b/130b,實作有效負載是翻倍的),而數位控制器內部有兩種方法:如果數據位寬固定都是32bit,那GEN1時core clock的速率為62.5MHZ,GEN2時為125MHZ,GEN3時為250MHZ;如果是clock速率保持為125MHZ不變,則GEN1時數據位寬為16bit,GEN2時為32bit,GEN3時為64bit。GEN3的芯片同時支持在GEN1和GEN2模式下執行,並且最開始初始化時即從GEN1開始,然後硬體雙方進行握手,看一起能支持的最大速率是多少,然後再調節到最大速率;如果在高速率下出現不穩定、自檢錯誤過多,還可以自動回退到低速率上安全執行。這樣的設計方式是非常合理的

同樣,對於Thunderbolt來說,GEN1是10Gbps X1,GEN2是10Gbps X2, GEN3是20Gbps X2,它本身是可以執行在GEN1 10Gbps,接在USB3.1-C介面上時,是以USB 3.0的控制器協定執行的,也就是5G的速度,並不是USB 3.1 10G,這點是最近幾天看到資料才知道的。這麽做應該是出於設計成本和穩定性的考慮吧,畢竟USB 3.1協定出來沒多久,設計公司還沒有成熟穩定的程式碼,那ThunderBolt 3.1就要使用USB 3.1的協定的話,設計ThunderBolt 3.1控制器部份時就比較困難了,還不如直接采用成熟的USB 3.0。這也從一個角度說明了,協定的設計是比較接地氣的,要考慮多方面的因素,而不是一昧地求新求快。

也有網友留言說現在Intel推出的控制器支持10G。anyway,PHY通道是支持的,這主要取決於控制器部份。

------------------------------------------------------------------------

Thunderbolt可以看成是PCIE GEN3與DisplayPort視訊接頭的合體,Thunderbolt控制器一端接PCIE數據流和DisplayPort數據流,一端連線PHY介面。控制器對進入的數據經過少量的處理,仍基本保持原來的數據格式形式,比如其中的PCIE 3.0數據仍為64b/66b或128b/130b編碼形式,而DisplayPort保持8b/10b編碼形式。

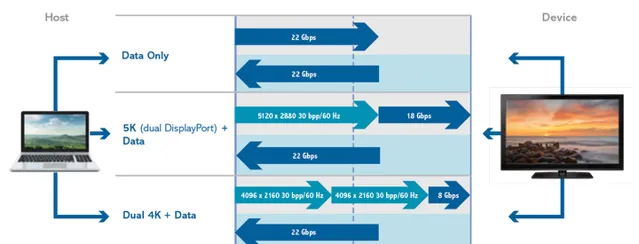

當同時連線PCIE裝置和DisplayPort裝置時,DisplayPort通道擁有更高的優先權,如下圖所示,Data Only時,下行和上行數據速度最大為22Gbps; 當接一個5K高畫質裝置時,下行數據速度減小為18Gbps,上行保持不變; 當接兩個4K高畫質裝置時,下行數據速度減小為8Gbps,上行保持不變。

從上可見,Thunderbolt 3.0單鍊結的速率就是20Gbps,這個對物理通道的要求是相當高的,通常銅介質做到16Gbps就很困難了(目前還有做到28G甚至30G以上的銅介質傳輸的報道),想要完美地執行如此高的速率,官方認證的原裝線纜必不可少,價錢也很昂貴羅。

覺得寫得不錯大家點個贊,說錯的地方請輕砸啊。